# **Study of Counter Circuits**

**Objectives:** To construct and study the operations of the following circuits:

- (i) A 4-bit binary ripple Up-counter

- (ii) A 4-bit binary ripple Down-counter

- (iii) A Mod-12 counter

#### **Overview:**

Binary Counters are one of the applications of sequential logic using flip-flops. A counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, in form of a clock pulse. Counters can be formed by connecting individual flip-flops together. On application of pulses, the flip-flops in the counter undergo a change of state in such a manner that the binary number stored in the flip-flops represents the number of pulses applied at input. When clock pulses are applied to a counter, the counter progresses from one state to another and the final output of the flip-flop in the counter indicates the pulse count. If all the flip-flops are not clocked at the same time, the counter is *asynchronous (or Ripple)* and if they are clocked simultaneously, the counter is *synchronous*. In practice, there are two types of counters:

- up counters, for increment in value

- down counters, for decrement in value

**Frequency Division:** For frequency division, toggle mode flip-flops are used in a chain as a divide by two- counter. One flip-flop will divide the input clock frequency by 2, two flip-flops will divide it by 4 (and so on). One benefit of using toggle flip-flops for frequency division is that the output at any point has an exact 50% duty cycle. The final output clock signal will have a frequency value equal to the input clock frequency divided by the MOD number of the counter. Such circuits are known as "divide-by-n" counters, where "n" is the number of counter stages used.

#### **Binary ripple Up-counter:**

We will consider a basic 4-bit binary up counter, which belongs to the class of asynchronous counter circuits and is commonly known as a ripple counter. Since a flip-flop has two states, a counter having n flip-flops will have 2<sup>n</sup> states. Hence, in this case the counter will have 2<sup>4</sup> or 16 states.

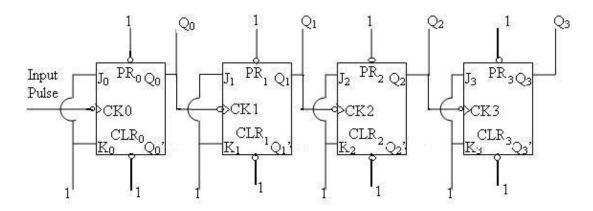

The schematics below shows a 4-bit up-counter implemented with four JK flipflops. It can be noticed that the normal output of each flip-flop is connected to the clock input of next flip-flop. Please recall that in case of JK flip-flop, with J=K=1, if an input clock pulse is supplied, the output toggles during the positive or negative (which is the case here, i.e. transition of pulse from 1 to 0) edge of the pulse. The count held by this counter is read in the reverse order from the order in which the flip-flops are triggered. Thus, output  $Q_3$  is the highest order of the count, while output  $Q_0$  is the lowest order. The binary count held by the counter is then  $Q=Q_3Q_2Q_1Q_0$ .

Let us start from the reset condition of all the flip-flops so that counter reads 0000 (decimal 0). When the trailing or negative end of the first pulse arrives, the first flip-flop gives an output  $Q_0=1$ , which does not affect the second flip-flop and the counter reads 0001. The counting sequence corresponding to each input pulse is summarized in the table below. On supplying 15<sup>th</sup> pulse the counter reads 1111 (decimal 15). The next clock pulse after count 1111 will cause the counter to try to increment to 10000 (decimal 16). However, that 1 bit is not held by any flip-flop and is therefore lost. As a result, the counter actually reverts to 0000, and the count begins again.

### **Circuit Diagram:**

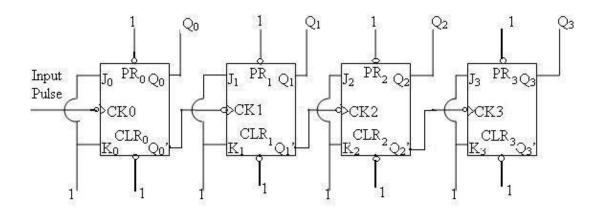

#### **Binary ripple Down-counter:**

The binary ripple down-counter decreases the count by one each time a pulse occurs at the input. The only difference it has from the up-counter is that the complement output of one flip-flop is connected to the clock input of the subsequent flip-flop. Here the complement output toggles at each negative edge of the clock pulse (1 to 0 transition), which is equivalent to a normal output toggling for positive edge of the clock pulse (0 to 1 transition). The counter starts from 1111 with the first pulse after it is reset and reverts back to 0000 after 15 pulses.

#### **Circuit diagram:**

**Characteristic Tables:**

# **UP COUNTER**

#### **DOWN COUNTER**

| Input | <b>Binary count</b>   |                       |                       |                       | Decimal   | Input | <b>Binary count</b>   |                       |                       | Decimal count         |           |

|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------|

| pulse | <b>Q</b> <sub>3</sub> | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>1</sub> | $\mathbf{Q}_{0}$      | count     | pulse | <b>Q</b> <sub>3</sub> | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>1</sub> | <b>Q</b> <sub>0</sub> |           |

|       | <b>2</b> <sup>3</sup> | 2 <sup>2</sup>        | <b>2</b> <sup>1</sup> | <b>2</b> <sup>0</sup> |           | 0     | 0                     | 0                     | 0                     | 0                     | 0         |

| 0     | 0                     | 0                     | 0                     | 0                     | 0         | 1     | 1                     | 1                     | 1                     | 1                     | 15        |

| 1     | 0                     | 0                     | 0                     | 1                     | 1         | 2     | 1                     | 1                     | 1                     | 0                     | 14        |

| 2     | 0                     | 0                     | 1                     | 0                     | 2         | 3     | 1                     | 1                     | 0                     | 1                     | 13        |

| 3     | 0                     | 0                     | 1                     | 1                     | 3         | 4     | 1                     | 1                     | 0                     | 0                     | 12        |

| 4     | 0                     | 1                     | 0                     | 0                     | 4         | 5     | 1                     | 0                     | 1                     | 1                     | 11        |

| 5     | 0                     | 1                     | 0                     | 1                     | 5         | 6     | 1                     | 0                     | 1                     | 0                     | 10        |

| 6     | 0                     | 1                     | 1                     | 0                     | 6         | 7     | 1                     | 0                     | 0                     | 1                     | 9         |

| 7     | 0                     | 1                     | 1                     | 1                     | 7         | 8     | 1                     | 0                     | 0                     | 0                     | 8         |

| 8     | 1                     | 0                     | 0                     | 0                     | 8         | 9     | 0                     | 1                     | 1                     | 1                     | 7         |

| 9     | 1                     | 0                     | 0                     | 1                     | 9         | 10    | 0                     | 1                     | 1                     | 0                     | 6         |

| 10    | 1                     | 0                     | 1                     | 0                     | 10        | 11    | 0                     | 1                     | 0                     | 1                     | 5         |

| 11    | 1                     | 0                     | 1                     | 1                     | 11        | - 12  | 0                     | 1                     | 0                     | 0                     | 4         |

| 12    | 1                     | 1                     | 0                     | 0                     | 12        | - 13  | 0                     | 0                     | 1                     | 1                     | 3         |

| 13    | 1                     | 1                     | 0                     | 1                     | 13        |       | -                     | -                     |                       |                       |           |

| 14    | 1                     | 1                     | 1                     | 0                     | 14        | 14    | 0                     | 0                     | 1                     | 0                     | 2         |

| 15    | 1                     | 1                     | 1                     | 1                     | 15        | 15    | 0                     | 0                     | 0                     | 1                     | 1         |

| 16    | 0                     | 0                     | 0                     | 0                     | 0 (RESET) | 16    | 0                     | 0                     | 0                     | 0                     | 0 (RESET) |

### Modulus-12 Counters:

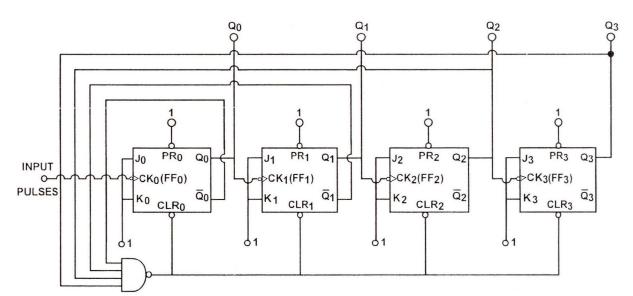

The modulus of a counter is the number of discrete states a counter can take up. A counter with n no. of flip flops will have  $2^n$  number of possible states. So counters with modulus, for example, 2, 4, 8, 16, can be built up using 1, 2, 3, 4 flip flops. It is quite often desirable to construct a counter having a modulus of 5, 9 or 12 etc. To design counters of modulus-12 (say), one has to use a modulus 16 counter and to arrange the circuit in such a way that

it skips some of its natural states restricting it to12. The simplest way of doing this is the direct clearing method, where a gate circuit is used to clear all the flip flops as the desired count is reached. Thus, for a modulus N counter, the number n of flip-flops should be such that n is the smallest number for which  $2^n$ >N and then to skip the surplus states with some rearrangements of the circuit.

The circuit diagram for a Mod-12 counter is shown below. It is obvious that a mod-12 counter will require 4 flip-flops which when connected as a counter, will provide 16 states. This counter counts 0, 1, 2, ..., 15 and then it resets to 0. For a mod-12 counter, one may skip state 12 and return to state 0 from state 11 and the cycle should continue this way. For this an additional combinational logic circuit, i.e. a 4-input NAND gate is required, whose output is connected to clear terminal of all the flip flops. This will feed a reset pulse to the counter during state 12 (1100) and immediately after state 11 (1011). The flip-flops are reset and the counter starts counting again.

### **Circuit diagram:**

## **Circuit components/Equipments:**

- 1. Resistors (1K $\Omega$ , 5 Nos)

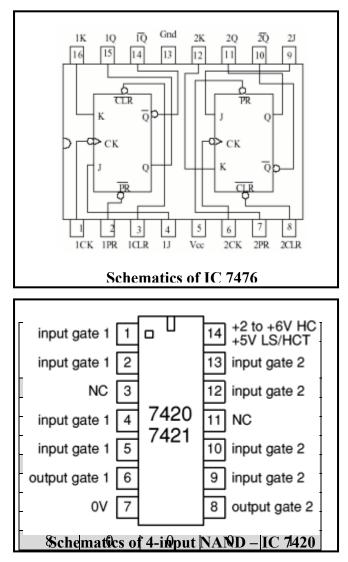

- 2. ICs [JK FF-7476, 2 Nos; OR-7432,1 No; 2-input AND- 7408, 2 Nos; 4-input NAND -7420, 1 No; NOT-7404, 1 No]

- 3. A Surface mount dip switch

- 4. D.C. Power supply (5V)

- 5. Function Generator

- 6. Oscilloscope

- 7. Red/Green LEDs (4 Nos)

- 8. Connecting wires

- 9. Breadboard

Circuit Diagrams: Already provided with text.

# **Procedure:**

- 1. Assemble the circuits one after another on your breadboard as per the circuit diagrams. Circuit diagrams given here do not show connections to power supply and LEDs assuming that you are already familiar with it from your previous lab experience. Here, all the LEDs are connected to the normal output of each flip flop. You will also use the oscilloscope to compare the timing diagrams of each of the output terminal and the input.

- 2. Connect the ICs properly to power supply and ground following the schematics for ICs given above.

- 3. Using dip switch and resistors, facilitate the required inputs from the power supply to the J, K, Pr and Cr terminals of the IC.

- 4. Use the function generator to facilitate clock pulse input to the circuit.

- 5. Turn on power to your experimental circuit.

- 6. Reset the circuit before applying pulse.

- 7. Set the function generator in "Pulse" mode by pressing the "Function" button. Set the frequency at a very low value (~ 1 Hz, amplitude ~ 5V) so that you can notice the logic states of the normal outputs indicated by the LEDs (ON = 1; OFF = 0).

- 8. The logic states of the J, K inputs must not be allowed to change when clock is high.

- 9. Record the normal output states of all the flip flops in a table for every pulse applied. Determine characteristic table for each operation.

- 10. Feed the input and each of the output of the up-counter to oscilloscope. Save the waveforms (Timing diagram) and compare their frequencies.

- 11. When you are done, turn off the power to your experimental circuit.

### **Observations:**

Table for ripple Up-counter:

Timing Diagram for up-counter:\_\_\_\_\_

Table for ripple Down-counter:

Table for Mod-12 counter:\_\_\_\_\_

### **Discussions:**

### **Precautions:**

- 1. Watch out for loose connections.

- 2. The logic states of the J, K inputs must not be allowed to change when clock is high.

#### Appendix: IC 7476 datasheet

|    | I   | nputs | Outputs |   |          |                    |  |

|----|-----|-------|---------|---|----------|--------------------|--|

| PR | CLR | CLK   | J       | к | Q        | a                  |  |

| L  | н   | Х     | Х       | Х | Н        | L                  |  |

| н  | L   | х     | X       | X | L        | Н                  |  |

| L  | L   | х     | X       | X | н        | н                  |  |

|    |     |       |         |   | (Note 1) | (Note 1)           |  |

| н  | н   | л     | L       | L | Qo       | $\overline{Q}_{o}$ |  |

| н  | н   | л     | н       | L | н        | L                  |  |

| н  | н   | л     | L       | н | L        | н                  |  |

| н  | н   | л     | н       | н | Toggle   |                    |  |

H = High Logic Level

L = Low Logic Level

X = Either Low or High Logic Level

\_r\_ = Positive pulse data. The J and K inputs must be held constant while the clock is high. Data is transferred to the outputs on the falling edge of the clock pulse.

Q<sub>0</sub> = The output logic level before the indicated input conditions were established.

Toggle = Each output changes to the complement of its previous level on each complete active high level clock pulse.

**Note 1:** This configuration is nonstable; that is, it will not persist when the preset and/or clear inputs return to their inactive (high) level.